# EE 505

Lecture 20

### ADC Design

- The Flash ADC

- Comparators

## Relative Statistical Characterization of R-based DACs

Resolution = 10

$A_{oR} = 0.02 \mu m$

$R_{\text{nom}} = 1000$

Total Area 2048 µm<sup>2</sup>

Resistor Sigma = 14.1421

$INL_{target} = 0.5 LSB$

Yield = 28.5%

| Architecture                      | INL(LSB) |       | DNL(LSB) |        | INL   |

|-----------------------------------|----------|-------|----------|--------|-------|

|                                   | Mean     | Sigma | Mean     | Sigma  | Yield |

| String                            | 0.385    | 0.118 | 0.049    | 0.0047 | 84.0  |

| Binary Weighted                   | 0.367    | 0.128 | 0.470    | 0.228  | 84.9  |

| R-2R Series                       | 0.609    | 0.295 | 1.021    | 0.610  | 41.4  |

| R-2R Parallel                     | 0.737    | 0.357 | 1.225    | 0.732  | 28.5  |

| Slice Scaled (1.7)<br>Series R-2R | 0.399    | 0.153 | 0.556    | 0.286  | 76.4  |

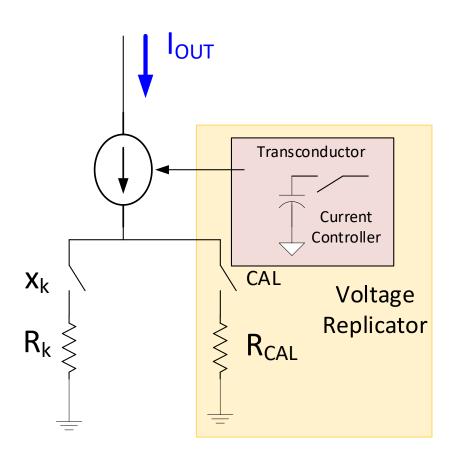

### Floating Current Copier

## **DAC** Architectures

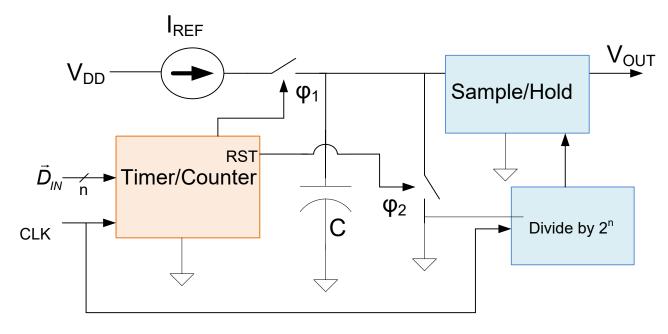

#### **Single Slope**

Single-Slope DAC

## **DAC Architectures**

#### **Single Slope**

Single-Slope DAC

Segmentation can be used to increase speed (I<sub>REF1</sub>=I<sub>REF</sub>/2^n<sub>1</sub>)

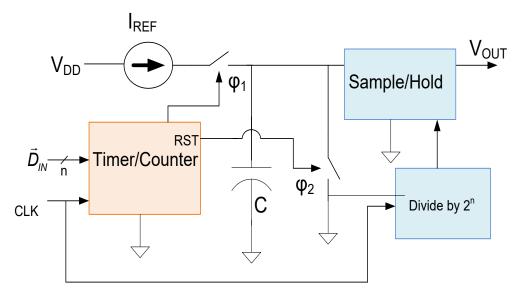

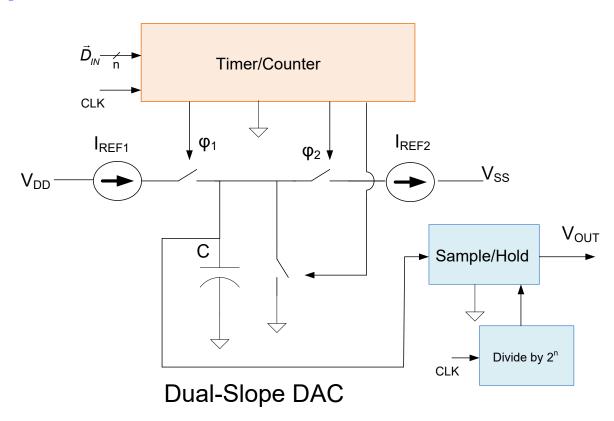

## **DAC** Architectures

#### **Dual Slope**

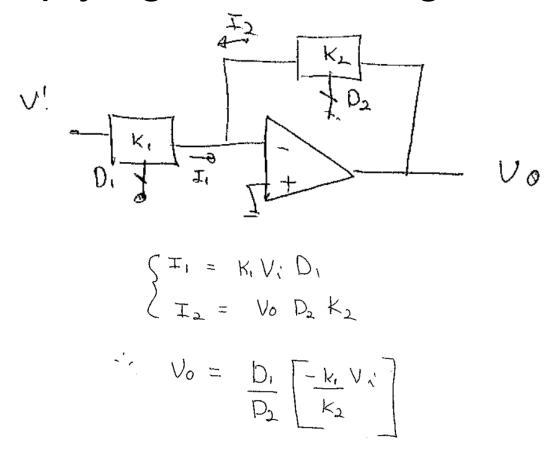

# Multiplying and Dividing DACs

Can create various nonlinear relationships with MDACs and Op Amps

# Analog to Digital Converters

The conversion from analog to digital in ALL ADCs is done with comparators

ADC design is primarily involved with designing comparators and embedding these into circuits that are robust to nonideal effects

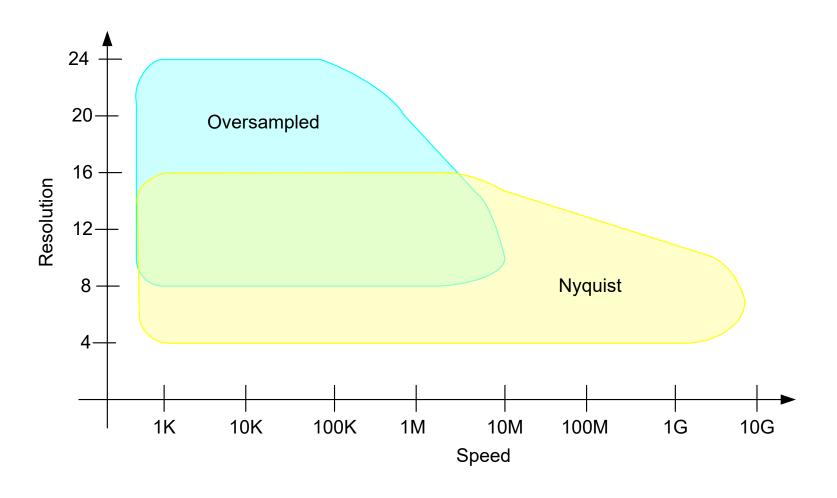

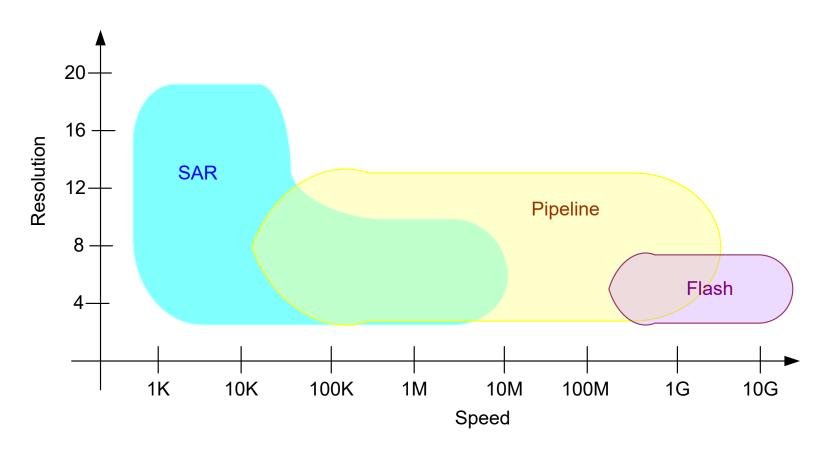

# Data Converter Type Chart

# Nyqyist Rate Usage Structures

Flash is the least used as a stand-alone structure but widely used as a subcomponent in SAR and Pipelined Structures

# **ADC Types**

#### **Nyquist Rate**

- Flash

- Pipeline

- Two-Step Flash

- Multi-Step Flash

- Cyclic (algorithmic)

- Successive Approximation

- Folded

- Dual Slope

#### **Over-Sampled**

- Single-bit

- Multi-bit

- First-order

- Higher-order

- Continuous-time

All have comparable conversion rates

Basic approach in all is very similar

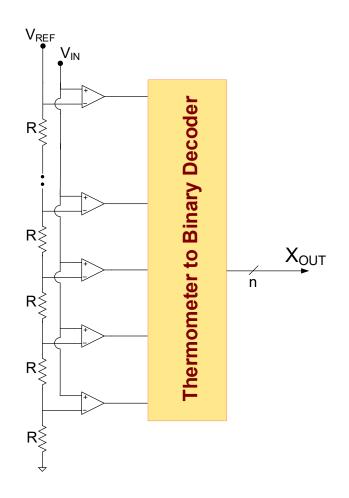

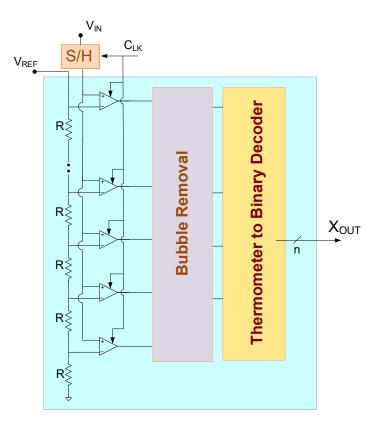

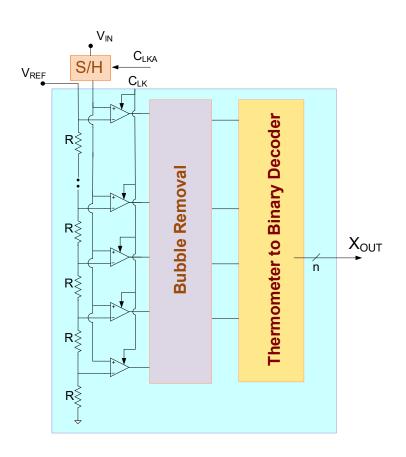

## Flash ADC

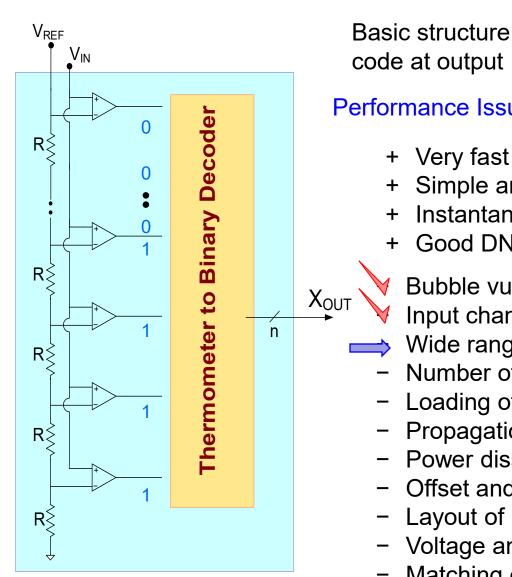

## Flash ADC

Basic structure has thermometer code at output

#### Performance Issues:

- + Very fast

- + Simple architecture

- Instantaneous output

- → Bubble vulnerability

- Input change during conversion

- Offset of comparators

- Number of components and area (for large n)

- Speed of comparators

- Loading of  $V_{REF}$  and  $V_{IN}$

- Propagation of V<sub>IN</sub> and Kickback

- Power dissipation (for large n)

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

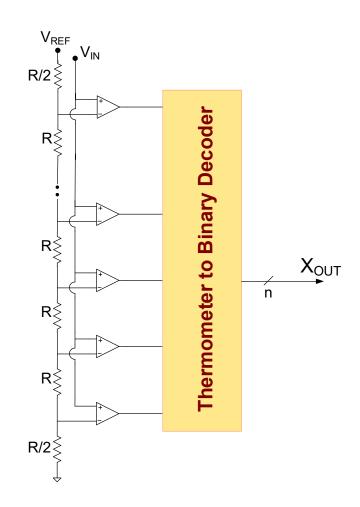

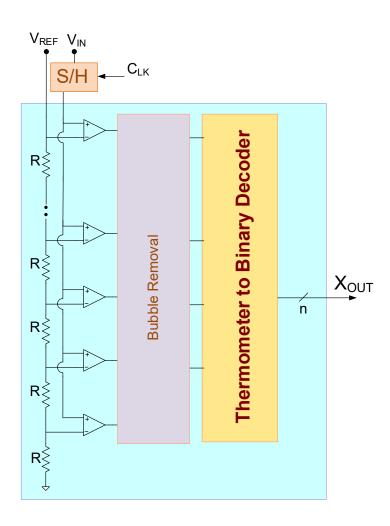

## Flash ADC

Basic structure has thermometer code at output

#### Performance Issues:

- + Very fast

- + Simple architecture

- + Instantaneous output

- → Bubble vulnerability

- Input change during conversion

- Offset of comparators

- Number of components and area (for large n)

- Speed of comparators

- Loading of  $V_{REF}$  and  $V_{IN}$

- Propagation of V<sub>IN</sub> and Kickback

- Power dissipation (for large n)

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

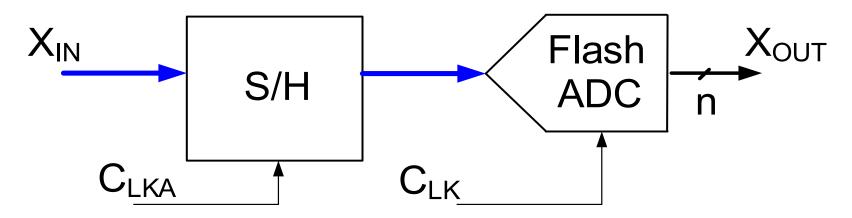

## Input change during conversion

Front-End S/H can mitigate effects of input change during conversion

- Speed of sample/hold of concern

- Noise of S/H

- Nonlinearity of S/H

- Input range of S/H

- Power dissipation of S/H

- Loose asynchronous operation of ADC

- Widely used

S/H may be most challenging part of design

## Input change during conversion

#### Flash ADC with Front-End S/H

## Input change during conversion

#### Flash ADC with Front-End S/H

Input S/H with Clk

Input S/H with Clk and clocked comparators

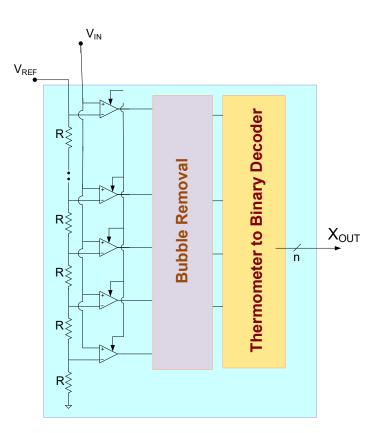

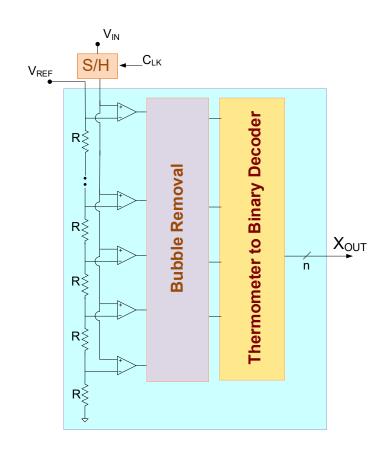

## Flash ADC

Basic structure has thermometer

#### Performance Issues:

- + Simple architecture

- + Instantaneous (asynchronous output)

- + Good DNL with low comparator offsets

**Bubble vulnerability**

Input change during conversion

Wide range of common-mode comparator inputs

- Number of components and area (for large n)

- Loading of  $V_{REF}$  and  $V_{IN}$

- Propagation of V<sub>IN</sub>

- Power dissipation (for large n)

- Offset and speed of comparators

- Layout of resistors

- Voltage and temperature dependence of R's

- Matching of R's

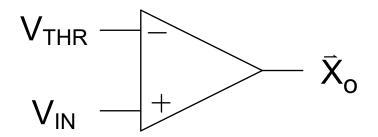

High gain amplifiers are often used as comparators since the outputs of most amplifiers naturally clip at high and low levels when overdriven

Since comparators are usually not used with feedback, there is not a need for compensation so neither the area reduction or speed reduction penalty is incurred

Since feedback is not used, higher-order amplifiers such as cascades can be used to increase the gain of a comparator to arbitrarily high levels

If over-driven amplifiers are used for comparators, the power dissipation of these types of comparators is often high

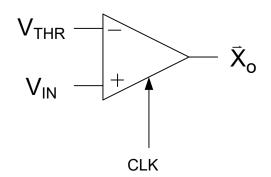

Some comparators are clocked and only provide an output after the transition of the clock

The value of the input to a clocked comparator is only of concern in a short time interval around the clock transition

The speed of clocked comparators can be very high and the power dissipation of clocked comparators can be very low

Clocked comparators are often called Dynamic Comparators

Regenerative feedback is often used in dynamic comparators and occasionally in non-clocked comparators

Dynamic comparators are widely used in the design of high-speed ADCs

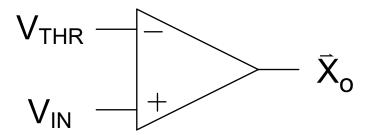

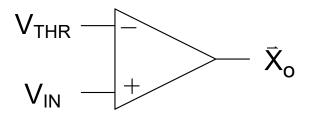

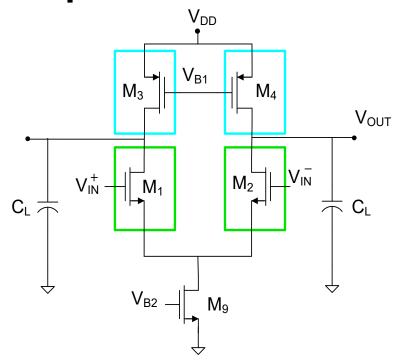

**Amplifier-Based Comparator**

**Amplifier-Based Comparator**

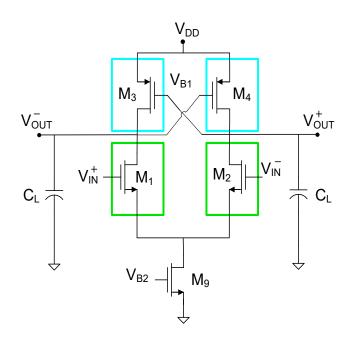

Note symmetry in the comparator

$$oldsymbol{v}_{d} = oldsymbol{v}_{in}^{+} - oldsymbol{v}_{in}^{-}$$

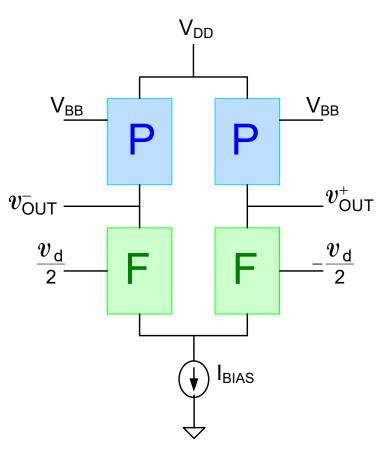

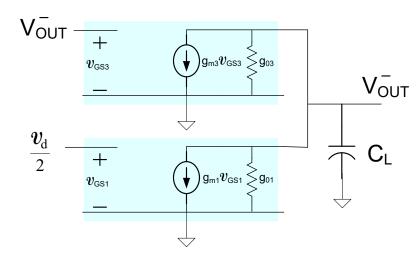

**Amplifier-Based Comparator**

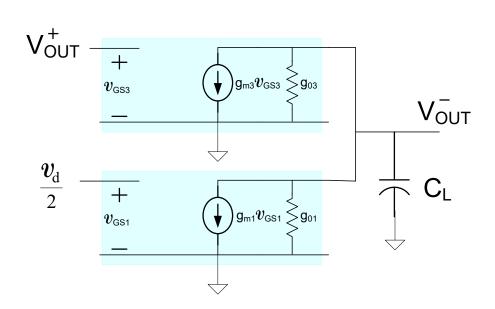

At the start of the comparison process, an amplifier-based comparator behaves as a linear amplifier

$$A(s) = \frac{v_{out}}{v_d} = \frac{1}{2} \frac{g_{m1}}{sC_L + g_{o1} + g_{o2}}$$

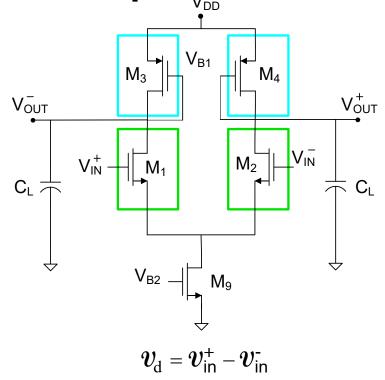

Lower-gain Amplifier-Based Comparator

$$v_{OUT}^{-}(sC_L + g_{o3} + g_{o1}) + g_{m1}\frac{v_d}{2} + g_{m3}(v_{OUT}^{-}) = 0$$

$$A(s) = \frac{v_{\text{out}}}{v_{\text{d}}} = -\frac{1}{2} \frac{g_{\text{m1}}}{sC_{\text{L}} + g_{\text{o1}} + g_{\text{o2}} + g_{\text{m3}}}$$

At the start of the comparison process, an amplifier-based comparator behaves as a linear amplifier

Lower-gain Amplifier-Based Comparator

Amplifier-Based Comparator with Regenerative Feedback

#### Amplifier-Based Comparator with Regenerative Feedback

At the start of the comparison process, an amplifier-based comparator behaves as a linear amplifier

#### Amplifier-Based Comparator with Regenerative Feedback

At the start of the comparison process, an amplifier-based comparator behaves as a linear amplifier

$$\begin{aligned} \boldsymbol{v}_{\text{OUT}}^{-} \left( \text{sC}_{\text{L}} + g_{\text{o}3} + g_{\text{o}1} \right) + g_{\text{m}1} \frac{\boldsymbol{v}_{\text{d}}}{2} + g_{\text{m}3} \left( -\boldsymbol{v}_{\text{OUT}}^{-} \right) &= 0 \\ \frac{\boldsymbol{v}_{\text{OUT}}^{-}}{\boldsymbol{v}_{\text{d}}^{-}} &= \frac{-\frac{g_{\text{m}1}}{2}}{\text{sC}_{\text{L}} + g_{\text{o}3} + g_{\text{o}1} - g_{\text{m}3}} \end{aligned}$$

Since  $g_m >> g_o$ , this comparator has a pole on positive real axis in the RHP Regenerative feedback will cause the output to latch at one of two levels But will not recover if small changes in input dictate a change in the output

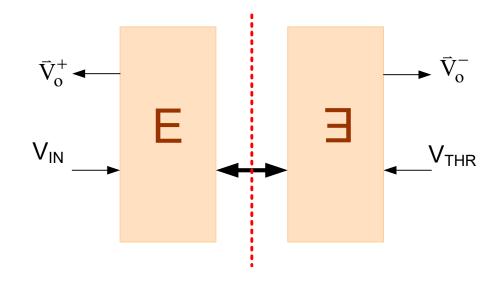

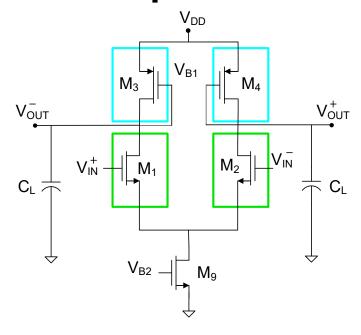

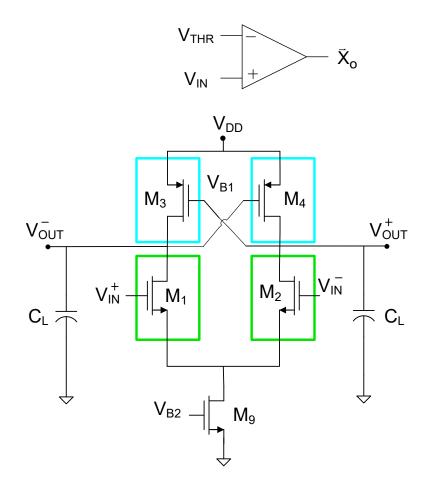

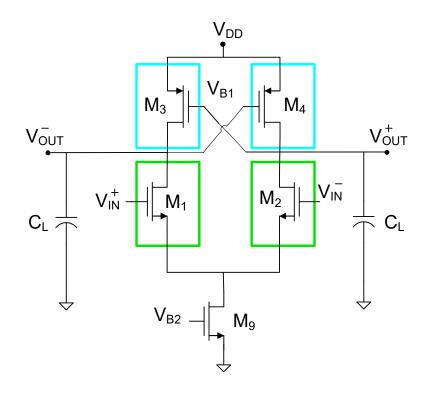

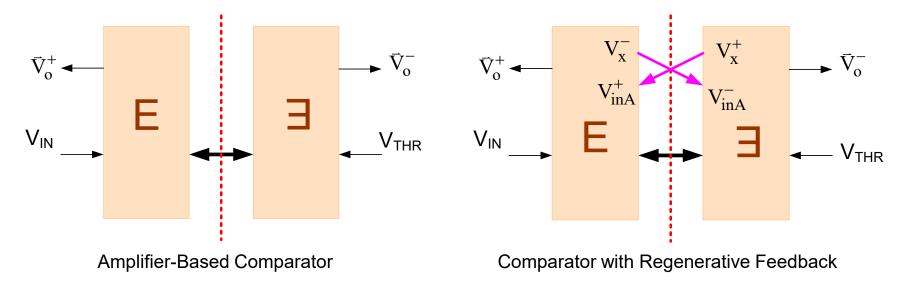

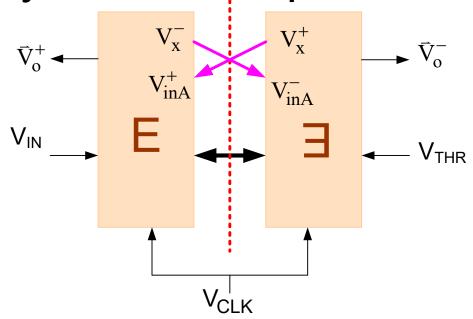

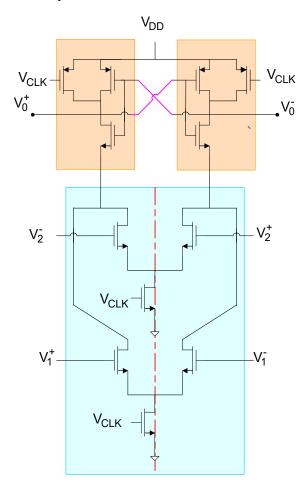

## Comparator Structures

Almost all comparators based upon two symmetric sub-circuits

Regeneration obtained by symmetrically cross-coupling across axis of symmetry from an output to an input

Any symmetric structure with this cross-coupling will create regenerative feedback but whether the poles move into the RHP depends upon the architecture

Clocks are often added to remove the restriction of regenerative-type structures not recovering when inputs change a little

Structure in upper right will be called a "Cross-Symmetric" structure

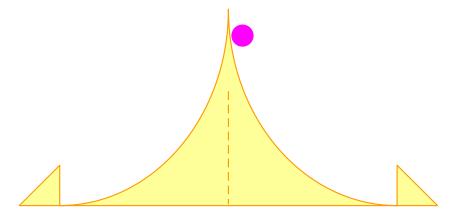

## Generic Dynamic Comparator Structure

Most circuits with this architecture that have a modest regenerative feedback gain will have a RHP positive real axis pole

All circuits with the cross-symmetric structure and a positive real axis pole can serve as dynamic comparators!

The clock is used to reset the circuit and thus to put it in a balanced state prior to regeneration

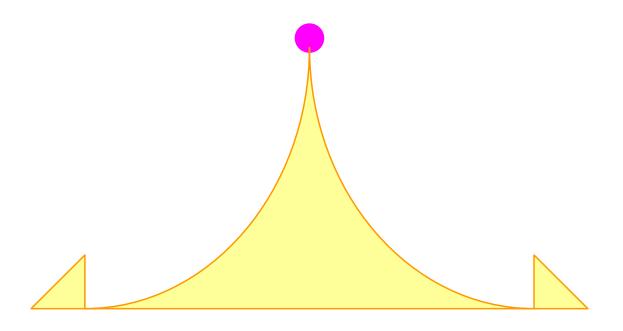

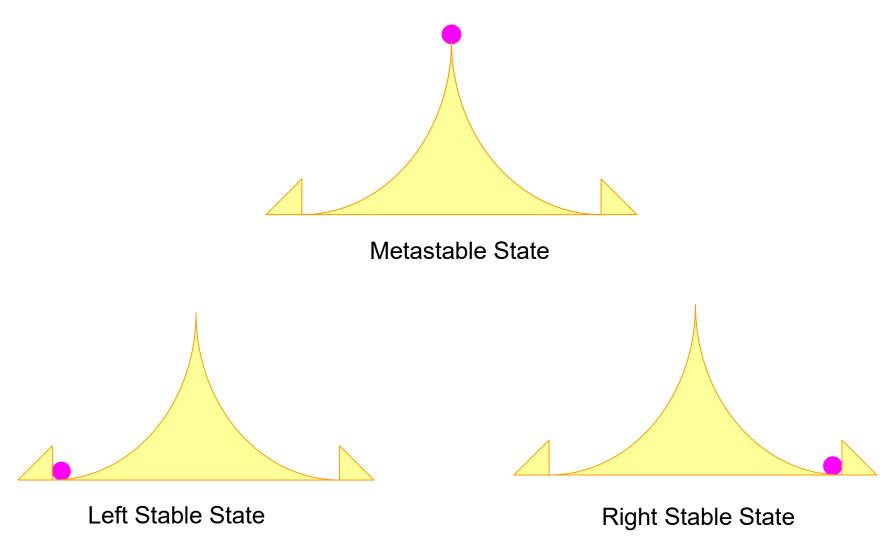

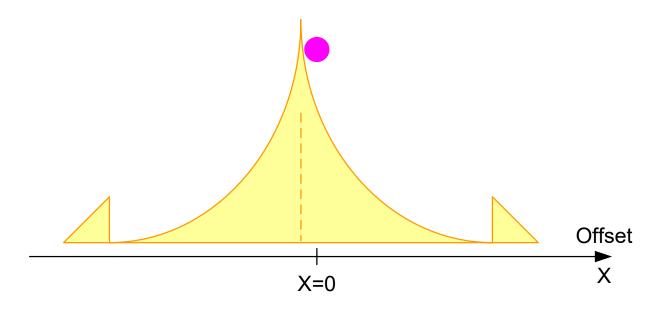

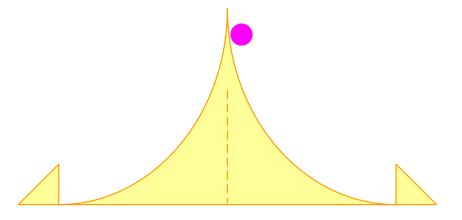

Ball in position shown is said to be in a metastable state

This system can not stay in this state indefinitely

A "reset" must be applied to put the system in the metastable state

- Given enough time, system will always enter one of the two stable states

- Time required to enter one of the two stable states is usually very small

- If at reset (ball at position x=0) the system is offset a small amount, a stable state will be reached very quickly

- Time required to enter one of the two stable states is usually very small

- The state it reaches tells whether the system offset is positive or negative

- The position of the ball after a small period of time provides a "boolean" output that gives the result of the comparison between the position of the ball and the position of the system

- This thus serves as a mechanical dynamic comparator

- Probability is 0 of having the initial offset be exactly 0

- Dynamic comparator will always make a decision

- But, if the offset is sufficiently close to 0, it may take a long time to make a decision

- In this mechanical system, the time it takes to make a decision is dependent upon the geometry of the system, the mass of the ball, and the coefficient of friction

- If the initial offset is uniformly distributed around x=0, for any time t, there is a small probability that the decision will not have been made at time t

- This probability is large if t is very small and is very small if t is large

- Some authors refer to the system being in a "metastable" state when a decision has not been reached but this term is misleading.

- If at any time t, the comparator has not made a decision, the system is in a transition state

- Most useful circuits that serve as dynamic comparators are very fast that is, they have a very high probability of making a decision in a very short time

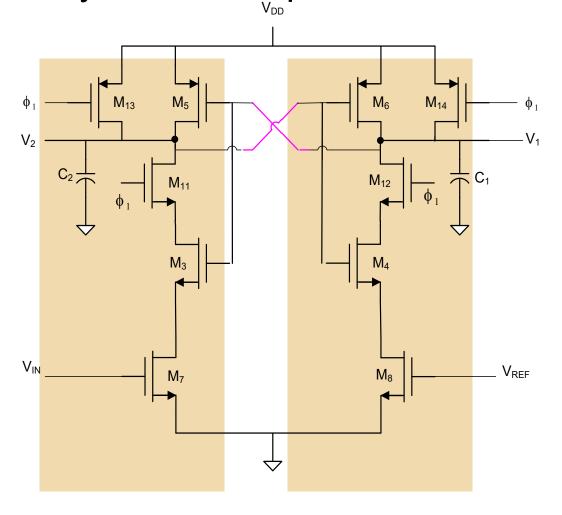

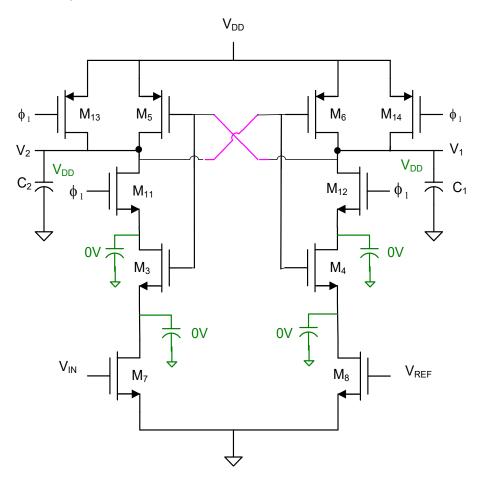

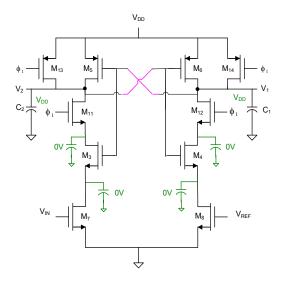

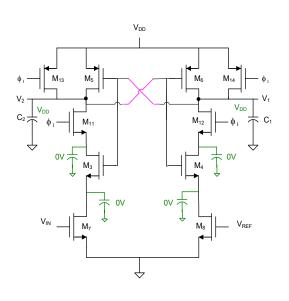

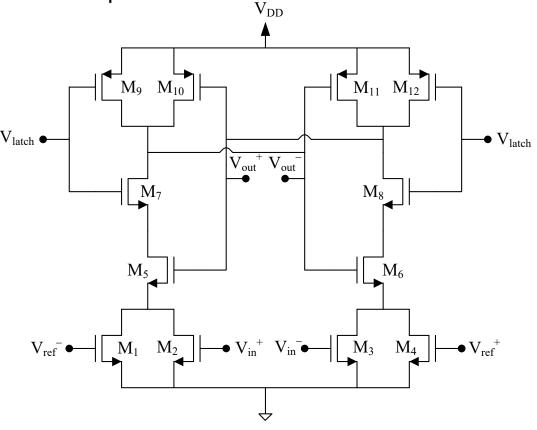

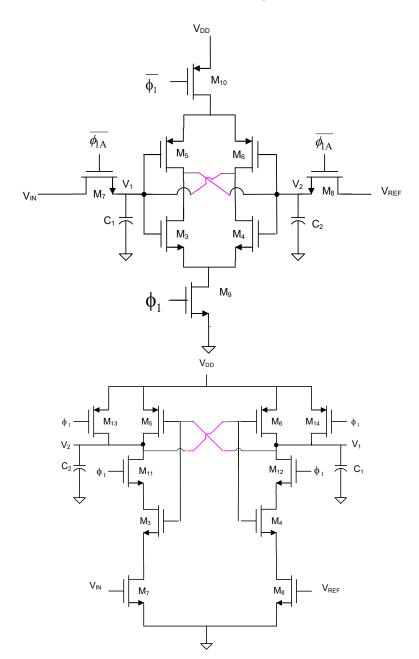

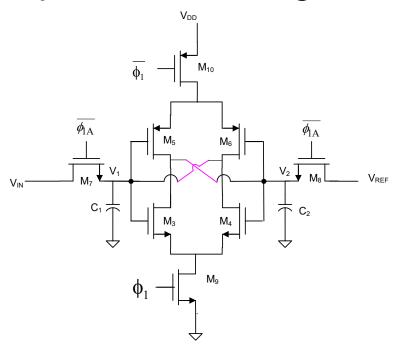

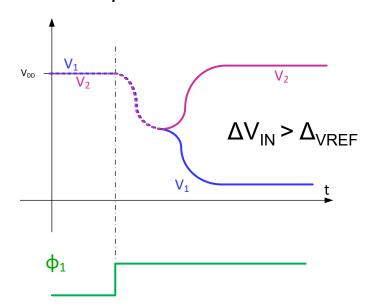

### Popular Dynamic Comparator Structure

#### Brief discussion of operation:

If  $V_{IN} > V_{REF}$  at the start of the evaluate state, the current in  $M_7$  will increase more rapidly than the current in  $M_8$ . Hence the current in  $M_5$  will cause the magnitude of  $V_{GS}$  on  $M_5$  to increase. This drives  $V_1$  down and ultimately  $V_2$  up

## Popular Dynamic Comparator Structure

Load can be viewed as two cross-coupled Boolean inverters Note zero static power dissipation

- Load can be viewed as two cross-coupled Boolean inverters

- Note zero static power dissipation!

- Reset precharges

- ${}^{ullet} V_1$  and  $V_2$  to  $V_{DD}$

- the voltage on the source node of M<sub>1</sub> to 0V

- •The volgate on the source node of M<sub>3</sub> to 0V

- Note zero static power dissipation!

Note: Both outputs always start high and then transition

Note: Will always leave metastable region but will occasionally not leave region soon enough

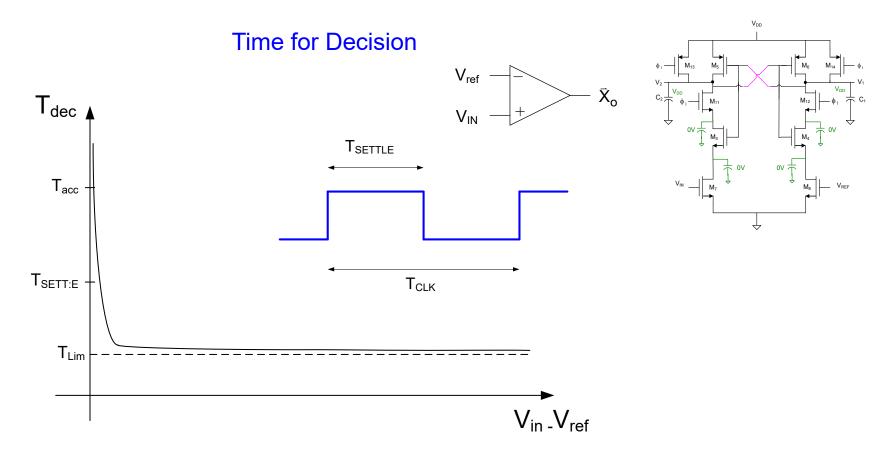

T<sub>acc</sub> is the maximum clock settling period that will give an acceptable probability of error in a comparator

T<sub>Lim</sub> is the limit of the settling time as the overdrive becomes large

• Note zero static power dissipation in the "arm" state!

- Reset sets inverter pair at trip point

- Note zero static power dissipation!

• Note zero static power dissipation!

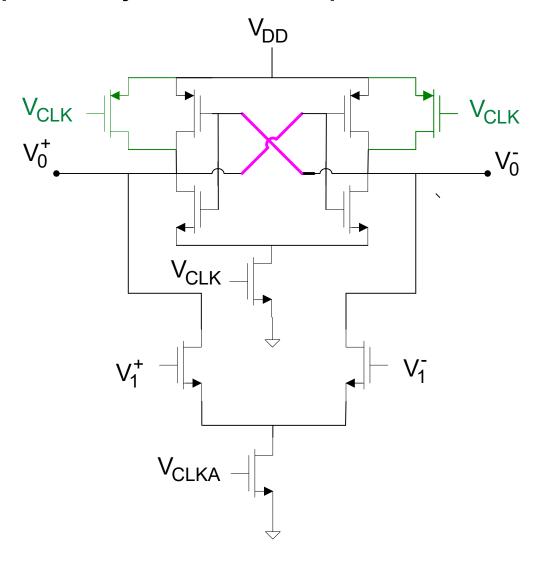

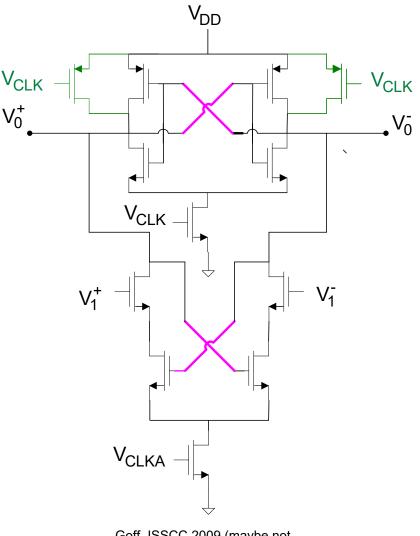

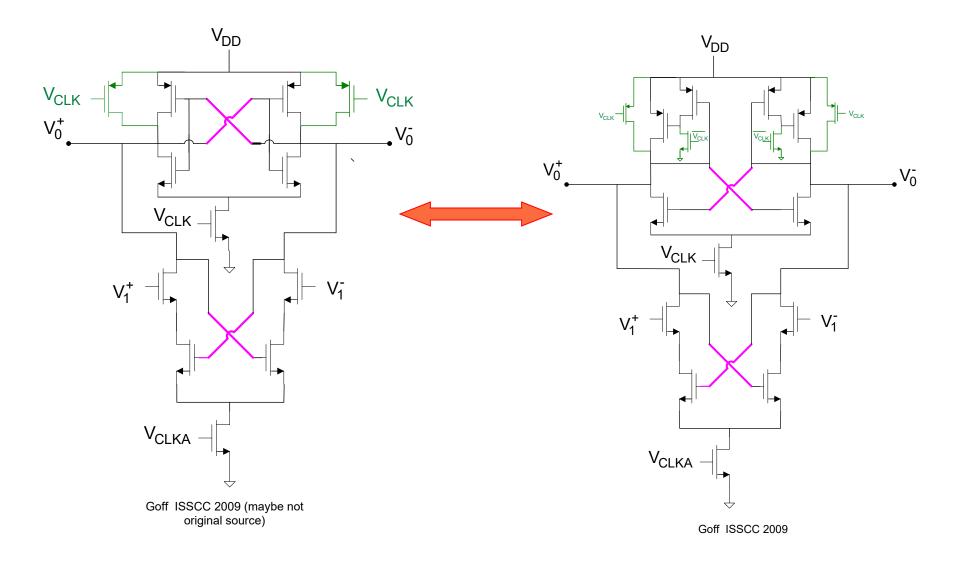

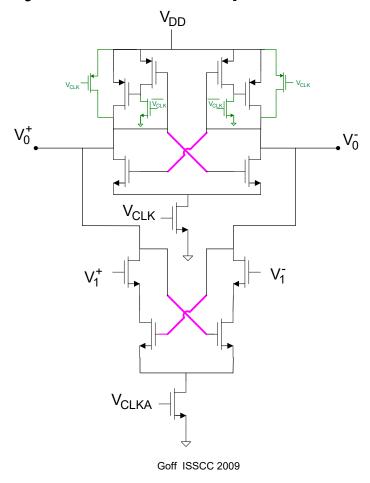

Goff ISSCC 2009 (maybe not original source)

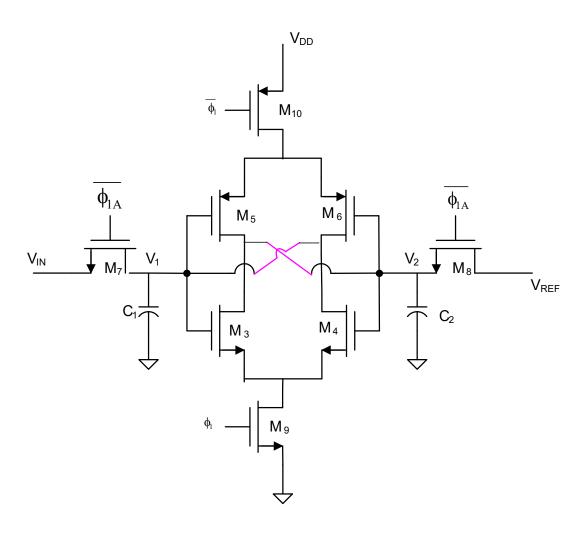

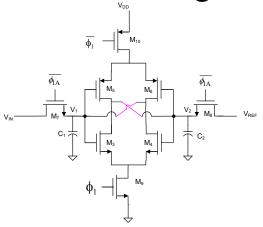

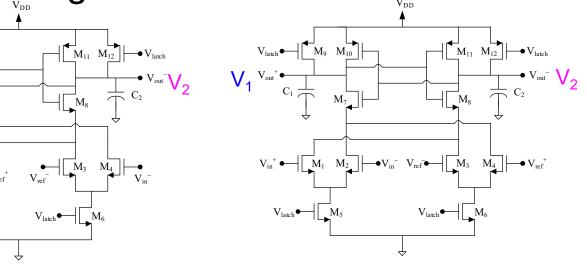

#### Alternate Dynamic Comparator Structure

How does this compare with the previous structure?

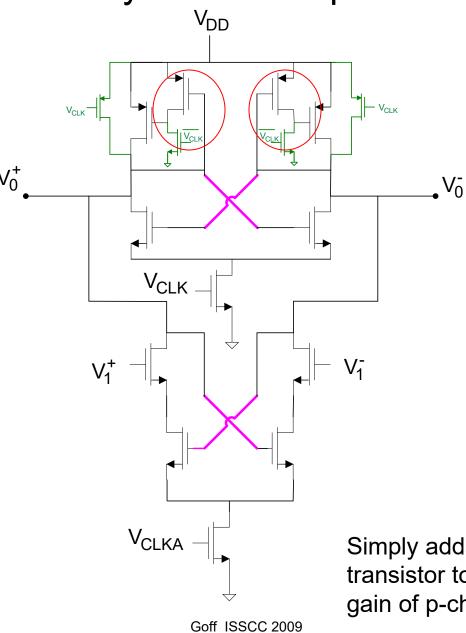

#### Alternate Dynamic Comparator Structure

Simply adds one more PMOS transistor to basic circuit to increase gain of p-channel load

#### Alternate Dynamic Comparator Structure

Natural questions arise -

If benefit was obtained from cascading p-channel devices in latch, how about cascading n-channel devices?

What about a fully-differential version of this concept?

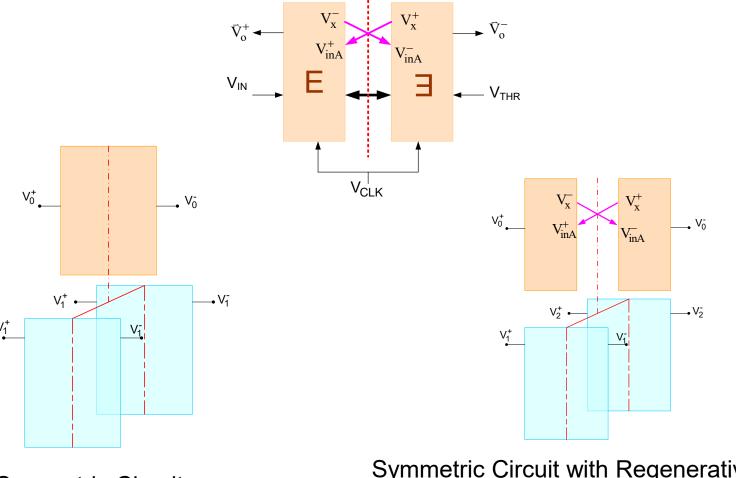

## Dynamic Comparator Structures

Symmetric Circuit (V<sub>CLK</sub> not shown)

Symmetric Circuit with Regenerative Feedback (V<sub>CLK</sub> not shown)

- Symmetric Circuit need not be planar

- Differential comparators often not planar

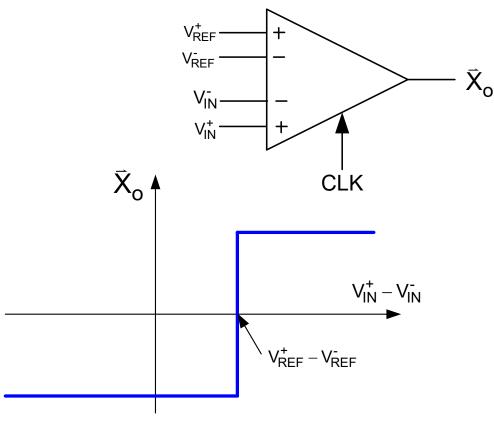

A differential comparator is a circuit that provides a high Boolean output if the differential input is positive and a low Boolean output if the differential

input is negative

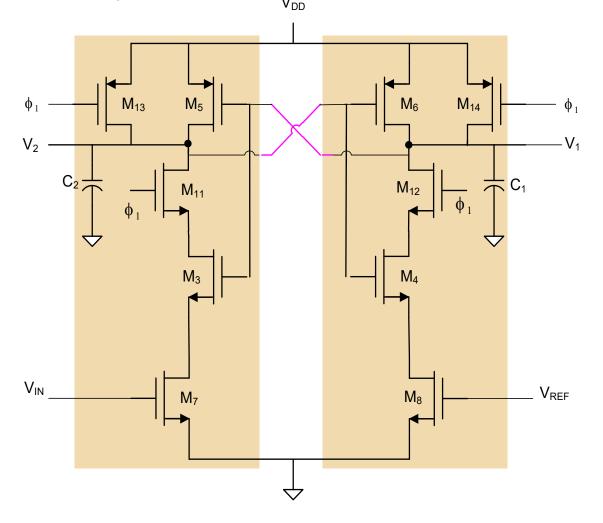

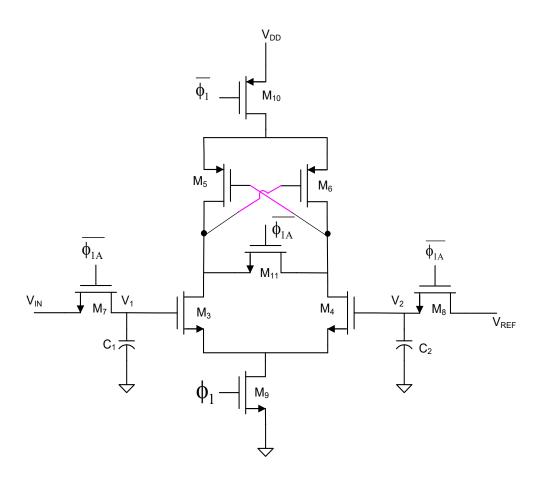

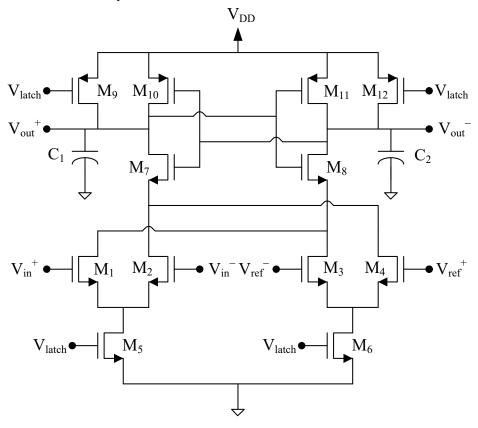

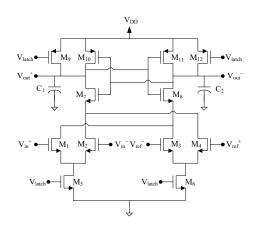

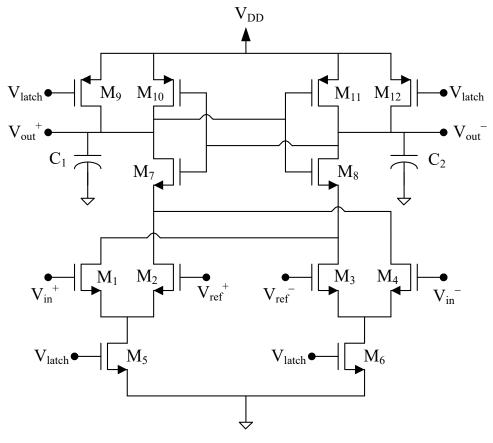

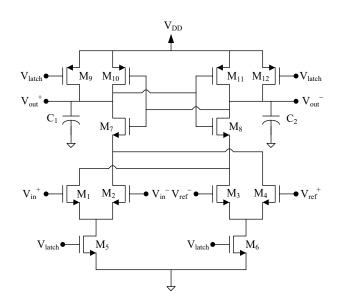

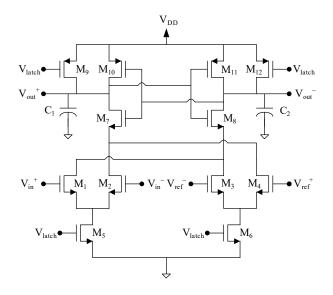

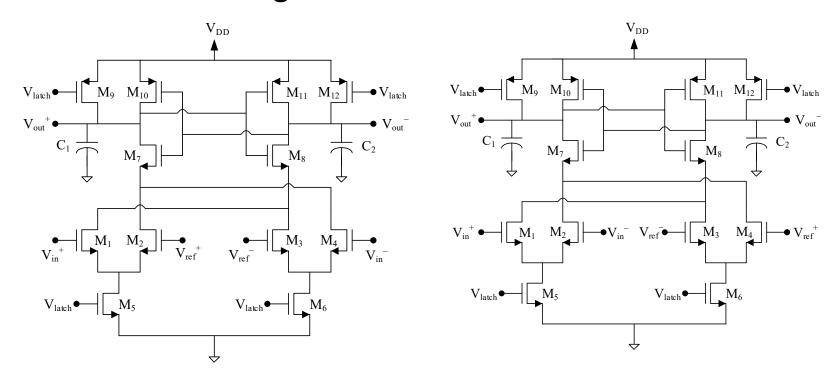

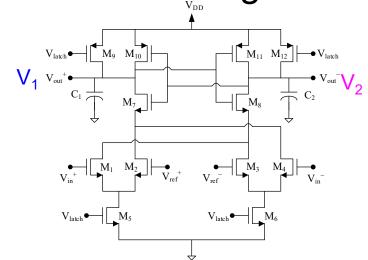

Popular differential comparator

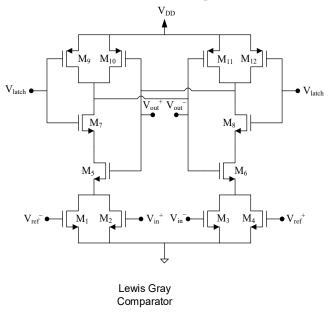

Lewis – Gray Comparator

Popular differential comparator

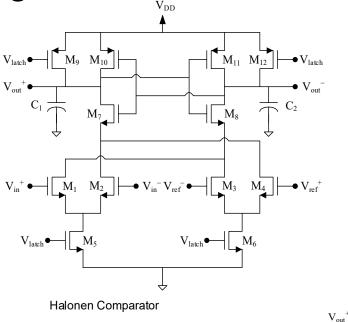

Halonen Comparator

Popular differential comparator

Halonen Comparator

Popular differential comparator

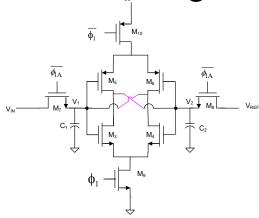

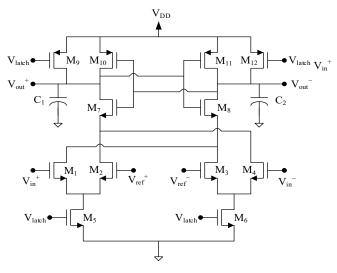

Katyal Comparator

## Dynamic Comparator Opportunities

- Dynamic Comparators can easily be designed

- Likely some of best structures have not evolved

- Symmetric circuit with regenerative feedback gives opportunity to identify new structures that may be particularly useful

Regenerative Feedback

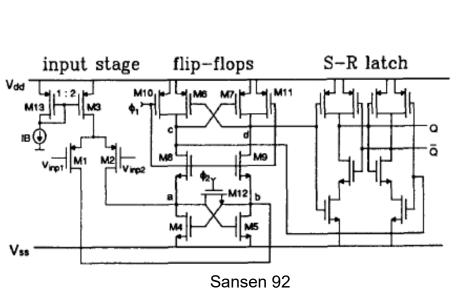

#### Regenerative Comparators

**Differential**

Single-Ended

- Regenerative feedback often used to force decision when differential inputs are small

- Several variants of clocked comparators are available

- Important to not have trip point dependent upon previous comparison results

- Often one or more linear gain stages precede the regenerative stage

- Power dissipation can be small in regenerative feedback comparators

- Large offset voltage (100mV or more) common for regenerative feedback comparators

Advanced clock samples inputs on input to digital latch cell During regenerative state power dissipation goes to 0 after decision is made

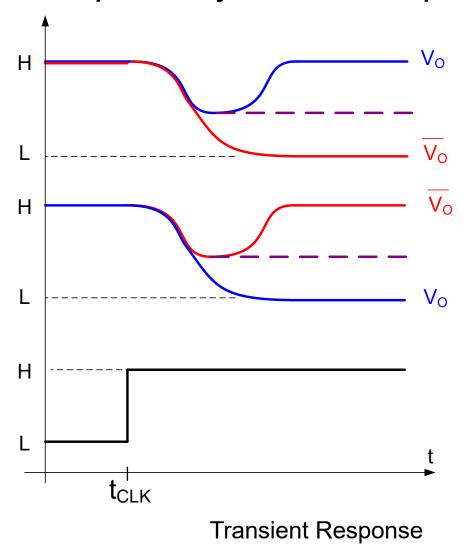

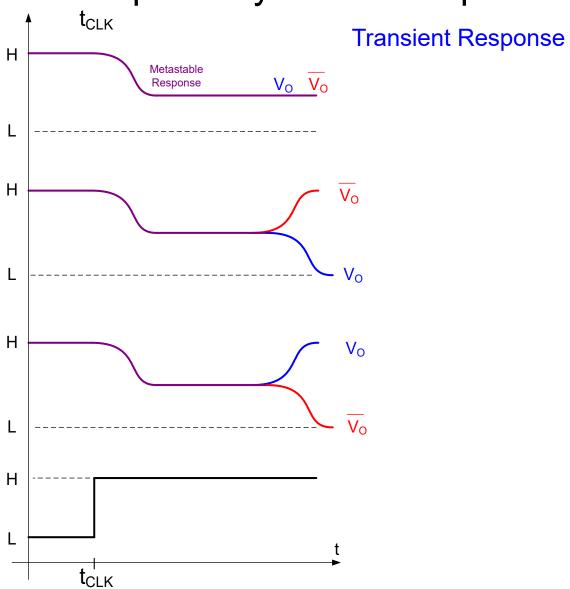

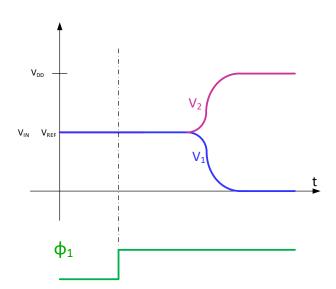

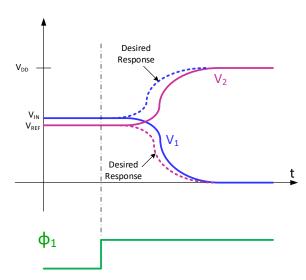

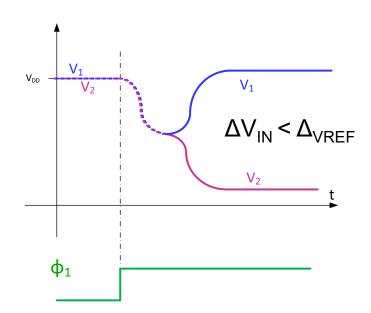

#### **Desired Response**

when  $V_{IN}$  and  $V_{REF}$  close to each other

- decision delayed

- may stay in metastable state until after decision must be made

- vulnerable to making wrong decision due to offset or noise

when  $V_{IN}$  and  $V_{REF}$  close to each other

- wrong decision when close (exaggerated)

- almost always only concerned about when  $V_{\text{IN}}$  close to  $V_{\text{REF}}$

#### Dominant causes of offset voltage of comparator

- Missmatch of parasitic capacitance on V<sub>1</sub> and V<sub>2</sub> nodes

- Missmatch in digital inverter trip points (particularly in weak inversion)

- Missmatch on advanced clocks (timing and parasitic capacitances)

- Missmatch of charge injection of advanced clocks

- Missmatch of leakage diffusion currents

- Assymetry in layout of cross-coupled structures

- Noise when in weak inversion

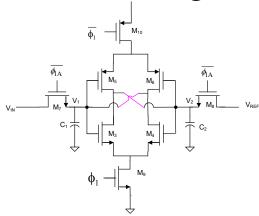

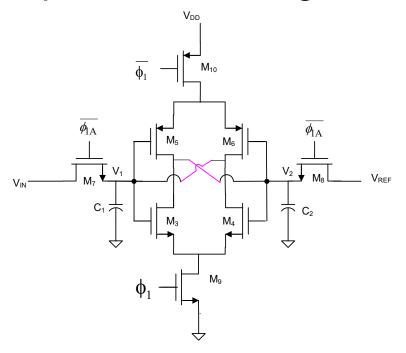

Katyal Comparator

### Katyal and Halonen Comparators with Regenerative Feedback

- Outputs precharge to V<sub>DD</sub>

- Current is steered to left or right side depending upon input differences

- Phasing of upper latch and lower latch signal may be different

- May limit swing on latch signals (switch versus current source in tail)

- $-\,$  Small previous-code dependence due to residual voltages on sources of  $\rm M_7$  and  $\rm M_8$

### Katyal and Halonen Comparators with Regenerative Feedback

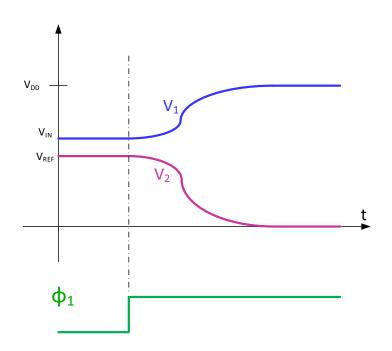

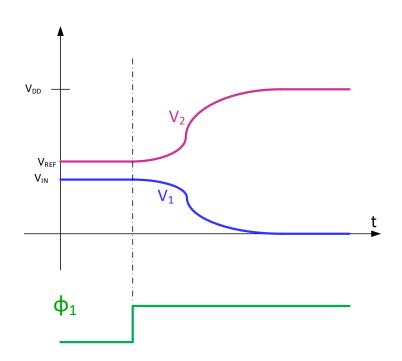

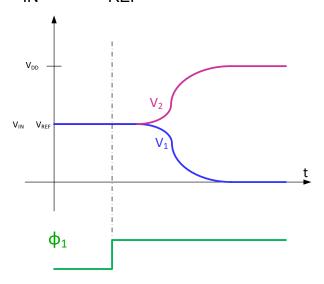

#### Ideal Responses

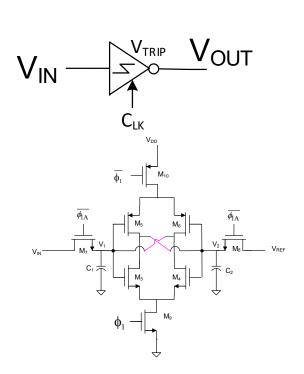

## Single-Ended Comparator w/o Reference

$$V_{IN} \xrightarrow{V_{TRIP}} V_{OUT}$$

$$V_{IN} \xrightarrow{V_{TRIP}} V_{OUT}$$

$$V_{TRIP} V_{OUT}$$

- Reference embedded in inverter trip point

- Device dimensions can set trip point

- Could be extremely small

- Highly dependent upon process variations

- Calibration can be used to trim trip points

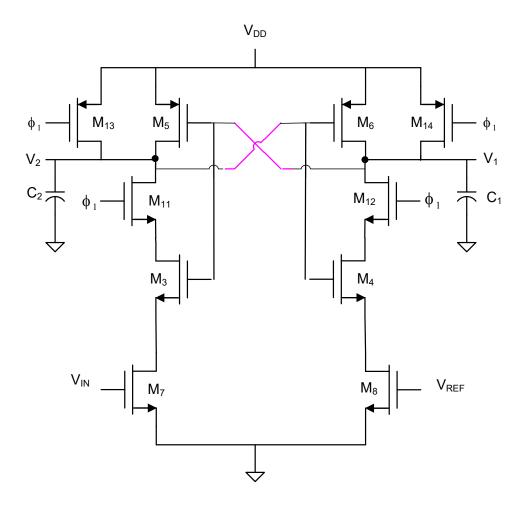

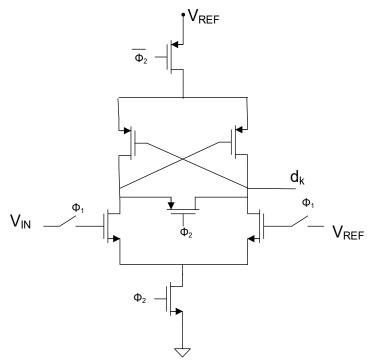

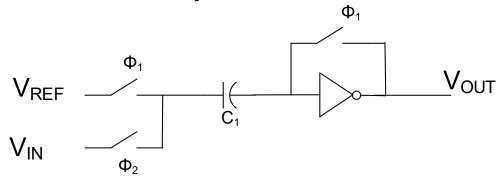

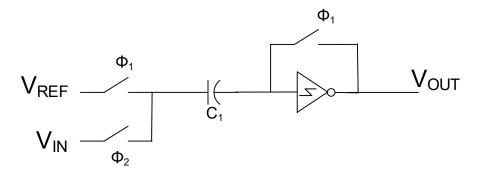

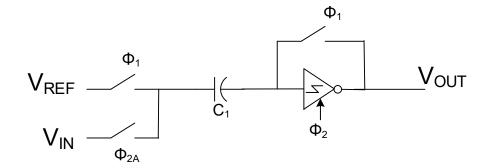

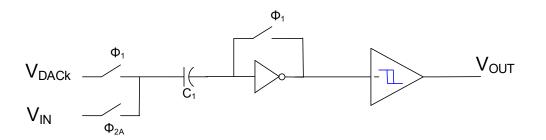

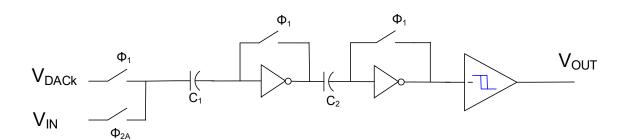

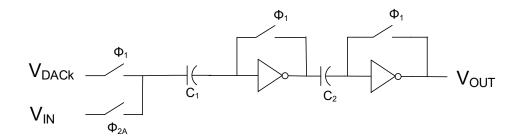

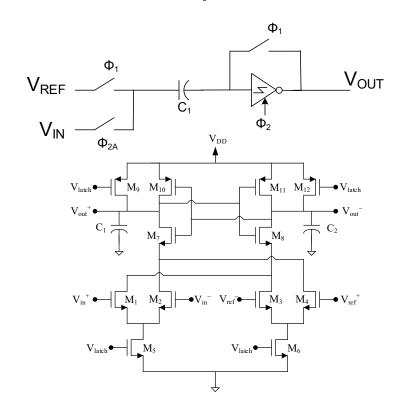

# Clocked Linear Comparator with Offset Compensation

Preamplifier or Linear Comparator with offset compensation

- Ideally removes all offset effects

- May not have a large enough gain

- Offset Compensation can be added to regenerative latches

- Several variants of offset compensation circuits are available

## Offset Compensation

Preamplifier or Regenerative Feedback can be added to amplifier

Comparator can be clocked following linear amplifier phase

# Some Variants of Clocked Offset Compensation

#### Where are poles of regenerative comparators located?

In RHP!

Is stability of concern?

No! Want positive real axis poles (i.e. unstable circuit) to force decision

Stay Safe and Stay Healthy!

## End of Lecture 20